分享文章

分享文章

酷睿Ultra 200V内核解密:四个E核略大于一个P核

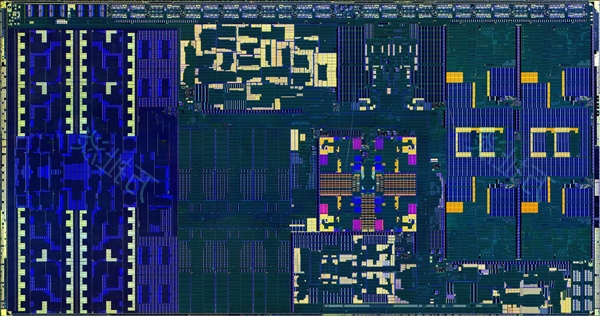

国外硬件专家Nemez利用B站网友“万扯淡”的底图,详细分析了Lunar Lake即酷睿Ultra 200V系列处理器的内部结构布局,其中大小核分布非常有意思。

酷睿Ultra 200V处理器分为计算模块、平台控制器模块,分别采用台积电3nm、6nm工艺,共同放置在台积电22nm制造的基底上。

计算模块面积为16.27×8.58=139.60平方毫米,平台控制器模块面积为11.51×3.97=45.69平方毫米,基底面积为16.77×13.10=219.69平方毫米。

每个核心自己有2.5MB二级缓存,也分成了两块。

旁边是四个为一组的Skymont架构的E核,集体共享12MB二级缓存,分成了三块。

对比来看,四个E核的面积稍微大于一个P核,这无疑是颇为值得称道的,因为上代四个E核面积约等于一个P核,而这一代E核的IPC性能整数提升了38%、浮点提升了68%,但面积却没有明显增大。

再往左是NPU AI引擎,分为六组NCE MAC阵列,每组猜测还是2MB缓存。

左侧边缘是GPU核显,一共八个Xe2 LPG架构的核心,以及分成两块的8MB二级缓存。

另外还有媒体引擎、显示引擎、8MB SLC系统缓存、128-bit LPDDR5X-8533内存控制器。

平台控制器模块内分布着PCIe 4.0/5.0控制器、雷电控制器、USB 3.x/2.0控制器、Wi-Fi与蓝牙控制器等。

平台控制器模块和和计算模块之间,通过两个模块桥接器(Tile Bridge)互相连接。

[超站]友情链接:

四季很好,只要有你,文娱排行榜:https://www.yaopaiming.com/

关注数据与安全,洞悉企业级服务市场:https://www.ijiandao.com/

关注网络尖刀微信公众号

关注网络尖刀微信公众号随时掌握互联网精彩

- 1 用创造拥抱新时代 7903978

- 2 外交部:不跪 7809305

- 3 高颜值副镇长直播把镇上花卖光 7713735

- 4 外国人为什么爱上来中国扫货 7616113

- 5 这个五一我选择反向出游 7523936

- 6 仝卓举报33家关联公司偷税漏税 7424118

- 7 章子怡因在领奖后台摔倒坐轮椅出行 7334045

- 8 曝董袭莹不符合“协和4+4”要求 7232652

- 9 董明珠年薪1437.2万 7141225

- 10 孙子随母姓 公公当众扇儿媳巴掌 7042811

塔塔

塔塔